* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Theory of Operations - University of Portland

Control theory wikipedia , lookup

Spectral density wikipedia , lookup

Voltage optimisation wikipedia , lookup

Three-phase electric power wikipedia , lookup

Power inverter wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Ground loop (electricity) wikipedia , lookup

Alternating current wikipedia , lookup

Transmission line loudspeaker wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Ringing artifacts wikipedia , lookup

Time-to-digital converter wikipedia , lookup

Electronic engineering wikipedia , lookup

Mathematics of radio engineering wikipedia , lookup

Mains electricity wikipedia , lookup

Chirp spectrum wikipedia , lookup

Buck converter wikipedia , lookup

Audio crossover wikipedia , lookup

Utility frequency wikipedia , lookup

Control system wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Schmitt trigger wikipedia , lookup

Regenerative circuit wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Power electronics wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Oscilloscope history wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

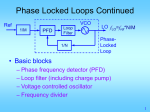

University of Portland School of Engineering 5000 N. Willamette Blvd. Portland, OR 97203-5798 Phone 503 943 7314 Fax 503 943 7316 Theory of Operations Project Cuckoo: Mixed Signal CMOS Phase-Locked Loop Contributors: Dan Booth Jared Hay Pat Keller Approvals Name Signature file Dr. Osterberg UNIVERSITY OF PORTLAND Date Date Name Signature file Dr. Lillevik SCHOOL OF ENGINEERING Date Date CONTACT: D. BOOTH, J. HAY, P. KELLER . . . . . Revision History . . Rev. Date. 0.9 02/06/03 . THEORY OF OPERATIONS PROJECT CUCKOO 0.91 1.0 02/07/03 01/13/03 UNIVERSITY OF PORTLAND REV. 1.0 PAGE II Author Team Cuckoo Team Cuckoo Team Cuckoo Reason for Changes Initial draft Add the conclusion Minor wording changes SCHOOL OF ENGINEERING CONTACT: D. BOOTH, J. HAY, P. KELLER . . . . . Table of Contents . . Summary....................................................................................................................... 1 . . Introduction .................................................................................................................. 2 THEORY OF OPERATIONS PROJECT CUCKOO REV. 1.0 PAGE III Background .................................................................................................................. 3 System Components................................................................................................... 4 General Description ................................................................................................................................4 Inputs and Outputs. .................................................................................................................................4 Frequency Generator .......................................................................................................................4 Oscilloscope .....................................................................................................................................5 Reset.................................................................................................................................................5 Divide-by-N Control ..........................................................................................................................5 Design Overview.......................................................................................................... 6 System Block Diagram............................................................................................................................6 Hardware Design ....................................................................................................................................7 Phase Frequency Detector ..............................................................................................................7 Low Pass Filter .................................................................................................................................7 Voltage Controlled Oscillator ....................................................................................................8 Frequency Divider .....................................................................................................................8 Conclusions ...............................................................................................................10 UNIVERSITY OF PORTLAND SCHOOL OF ENGINEERING CONTACT: D. BOOTH, J. HAY, P. KELLER . . . . List of Figures. . Figure 1. Block Diagram of.the complete system. ........................................................................................4 . Figure 2. Cuckoo system block . diagram.......................................................................................................6 THEORY OF OPERATIONS PROJECT CUCKOO UNIVERSITY OF PORTLAND REV. 1.0 SCHOOL OF ENGINEERING PAGE IV CONTACT: D. BOOTH, J. HAY, P. KELLER THEORY OF OPERATIONS PROJECT CUCKOO Chapter 1 . . . . . . . . . REV. 1.0 PAGE 1 Summary A Phase-Locked Loop (PLL) is a fundamental building block of many communication systems. It is comprised of a feedback loop system which produces an oscillating frequency that is matched in phase to a reference input frequency. The four building blocks of the PLL system are the phase frequency detector (PFD), loop filter, voltage controlled oscillator (VCO) and frequency divider (also called divide-by-n). A 1 kHz square-wave signal from 0 to 5 volts will be inputted from a frequency generator into the PFD of the PLL circuit. This signal will be compared with the output of the divideby-N of the feedback loop. The output of the PFD goes into a loop filter to generate a DC control voltage, and then the control voltage goes to the VCO. The output of the VCO is connected to the input of the divide-by-N, and to the oscilloscope. The oscilloscope will display the frequency of the VCO output signal. This system works because as the user changes the binary number that controls the divide-by-N, the two inputs to the PFD become slightly out of phase. This use of the feedback loop causes a change in the control voltage to the VCO, and subsequently changes the output frequency to correlate to the divide-by-N input so that the two inputs become “locked” at the new frequency. This is how our phase-locked loop will function. UNIVERSITY OF PORTLAND SCHOOL OF ENGINEERING CONTACT: D. BOOTH, J. HAY, P. KELLER THEORY OF OPERATIONS PROJECT CUCKOO Chapter 2 . . . . . . . . . REV. 1.0 PAGE 2 Introduction This document will cover many topics. First, we give the user information on the history of PLL’s, and why they are important. Then, we discuss how the system components are connected and how they are used. It gives parameters that the device needs to run under; if these requirements are not met, then the device may be damaged. Finally, we discuss the PLL itself. We give the theory of how the PLL works, a background on the different pieces, and how the pieces are connected. We not only tell how to make it work, but also why it works! This document does not cover how to debug the system if it does not work, except for how to use the reset. Team Cuckoo will generally be the only users of this project, UNIVERSITY OF PORTLAND and it will be used the SCHOOL OF ENGINEERING in the engineering building. CONTACT: D. BOOTH, J. HAY, P. KELLER THEORY OF OPERATIONS PROJECT CUCKOO Chapter 3 . . . . . . . . . Phase locked loop REV. 1.0 PAGE 3 Background (PLL) circuits are used in electrical systems to help stabilize frequencies. They are used in radios, televisions, telecommunications equipment, and computers for various uses such as frequency generation, demodulation, frequency tracking and clock recovery circuits. The first phase locked loop circuits were created as long ago as the 30’s, and have been widely used in consumer electronics such as radios and TVs since their invention. The essential PLL system can take a frequency, “lock” onto it and produce an output frequency that is in phase with the input. It accomplishes this by using feedback. This means that the output signal is constantly being compared against the input signal in order to maintain a stable or "locked” output. Depending on the specific needs of the system, the PLL can be digital, analog, or mixed-signal. The Phase-Locked Loop we are designing will be a mixed signal device and will be used as a frequency synthesizer. UNIVERSITY OF PORTLAND SCHOOL OF ENGINEERING CONTACT: D. BOOTH, J. HAY, P. KELLER THEORY OF OPERATIONS PROJECT CUCKOO Chapter 4 . . . . . . System Components . . . REV. 1.0 PAGE 4 General Description F r e q u e n c y PLL Divi debyN freq uen cy Co Figure 1. Block Diagram of the complete system. ntro l Res et O s c i l l o s c o p e G e n e r a t o r Our system consists of four major components. The components are the frequency generator, PLL, oscilloscope, reset, and divide-by-N frequency control. diagram shows how the are connected. This block The three inputs are from the frequency generator, reset, and the divide-by-N. The output will go to the oscilloscope. Inputs and Outputs. Frequency Generator The frequency generator should be set to a 1kH square wave with a voltage of 0 to 5 volts peak-to-peak. This output will connect to the input of the PLL circuit, or more specifically, to the phase frequency detector of the CMOS chip. UNIVERSITY OF PORTLAND SCHOOL OF ENGINEERING CONTACT: D. BOOTH, J. HAY, P. KELLER . . . . Oscilloscope . . . The oscilloscope . will read frequency that the voltage-controlled oscillator is outputting to . the frequency divider. The frequency is displayed on the oscilloscope for the user to see. THEORY OF OPERATIONS PROJECT CUCKOO REV. 1.0 PAGE 5 It has a high input impedance, so the signal to the frequency divider should not be affected. Reset The reset control is connected to all the flip-flops within the PLL circuit. The reset is only used if the system does not work because a flip-flop starts in an unknown state that causes problems. If there are problems on start-up, the reset button should be set to 0 (because it enable-low) momentarily to reset all the flip-flops. It should be set to 1 otherwise. Divide-by-N Frequency Control The divide-by-N control will be a binary number ranging between 90 and 110. The user inputs this number through a series of switches or buttons, and it will be displayed to the user via three seven-segment displays. It will input into the frequency divider in the CMOS chip. Although it is specified to be set between 90 and 110, it will have the capabilities of ranging from 2 to 127. UNIVERSITY OF PORTLAND SCHOOL OF ENGINEERING CONTACT: D. BOOTH, J. HAY, P. KELLER THEORY OF OPERATIONS PROJECT CUCKOO Chapter 5 . . . . . . . . . REV. 1.0 PAGE 6 Design Overview System Block Diagram R e f e r e n c e F r e q u e n c y i n P h a s e f r e q u e n c Cy M Od Se t e Cc ht io r p Our phase locked L o w V C O p a s s F rf ei ql ut ee nr D c i y v i d d i e F r e q u e n c y O u t v i b block diagram. Figure 2. Cuckoo system d y e loop design will take r N an input frequency, and create a square wave C output signal that is N times the input(frequency, where N is a selectable integer multiple. o n The Phase Locked Loop operates bast follows: The input “reference” signal and the y r o feedback signal both pass into the phase detector where a control voltage (CV) is N l ) generated which is proportional to the phase difference of the two signals. This CV then passes through a low-pass filter. The filtered signal is then used as the input to a voltagecontrolled oscillator (VCO), which generates the output signal. The feedback signal is taken from the output, passes through a frequency divider and back into the phase detector. UNIVERSITY OF PORTLAND SCHOOL OF ENGINEERING CONTACT: D. BOOTH, J. HAY, P. KELLER . . . . The phase frequency detector and frequency divider are implemented with digital CMOS . . the loop filter is made up of discrete analog components and the VCO is an logic, whereas . . off the shelf component manufactured by Exar. . THEORY OF OPERATIONS PROJECT CUCKOO REV. 1.0 PAGE 7 Hardware Design Phase Frequency Detector The phase detector takes two input signals and generates an output voltage that is proportional to the phase difference of the two input signals. The output of the PFD depends not only on the phase error but also on the frequency error, when the PLL has not yet acquired lock. The positive-going transients of the input signals determine the actual state of the PFD, which can take on one of three possibilities: logic high, logic low or high impedance. The two input signals trigger two flip-flops: While signal one leads signal two, the output of the PFD is logic high. While signal two is leading signal one, the output of the PFD is logic low. If the two signals are in phase, the output of the PFD is high impedance. This then passes to the low pass filter that converts the pulsed signal to a dc voltage. Low Pass Filter The low pass filter is described as a “passive lag-lead” filter. It is comprised of two series resistors and a parallel capacitor. They are commonly referred to as a charge pump because voltage is constantly being pumped into and out of the capacitor. When the incoming signal from the PFD is logic high, the capacitor charges up, increasing the output control voltage. When the incoming signal is logic low, the capacitor discharges across the resistors, lowering the output voltage. When the incoming signal is high impedance, the output voltage is held steady because the capacitor has nowhere to discharge. If the capacitor loses its charge (leakage to external components), the output voltage will lower, UNIVERSITY OF PORTLAND SCHOOL OF ENGINEERING CONTACT: D. BOOTH, J. HAY, P. KELLER . . . . and the feedback of the system will cause the output of the PFD to switch to logic high, . . capacitor and increasing the output voltage. recharging the . . . Voltage Controlled Oscillator THEORY OF OPERATIONS PROJECT CUCKOO REV. 1.0 PAGE 8 Exar 2209 VCO chip, see document “xr2209v202.pdf” The VCO accepts the output voltage of the loop filter as its control voltage. The VCO will be set with a free running frequency of 90kHz so that it will operate at 90kHz with no control voltage. As the control voltage increases, the output frequency will increase towards 110kHz. The sweep range must also be set such that a range of 20 kHz is obtained with our approximate control voltage range of 1-4 volts. Frequency Divider The frequency divider must by able to divide the VCO output by a factor varying from 90 to 110. It operates on the principle that if the rising and falling edges of the incoming square wave are counted then an output frequency can be generated from this by switching the output every so many “edges.” This is accomplished with the use of the following subcomponents: Edge counter The edge counter takes the incoming square wave and creates a pulse train with a pulse occurring on every rising or falling edge of the incoming square wave. 7-bit counter The 7-bit counter continuously counts upward with the pulse train from the edge counter serving as the clock. It is reset back to zero whenever the “divide by N control” binary input matches the counter output. This “match” is watched for by the comparator sub- UNIVERSITY OF PORTLAND SCHOOL OF ENGINEERING CONTACT: D. BOOTH, J. HAY, P. KELLER . . . . component which is what sends a reset to the counter. A “match” in the comparator sub. . a state change on the output frequency. section also triggers . . The output of.the 7-bit counter is a 7-bit binary number. THEORY OF OPERATIONS PROJECT CUCKOO REV. 1.0 PAGE 9 Synchronizer The output from the 7-bit binary counter goes into a synchronizer circuit that consists of seven D flip-flops, one for each bit. The flip-flops hold the output of the counter until it has settled and then pass the output on to the comparator. The same pulse train that is generated by the edge counter triggers the D flip-flops. This sub-component is necessary in order to get rid of “glitches” in the output of the frequency divider. Comparator The last component of the Frequency divider is the comparator. This takes the input form the divide by n control and the output of the synchronizer and compares the two. When a match occurs a reset signal is sent to the counter, this sends the counter into another loop. At the same time, the output of the comparator is toggled from 0 to 1, or from 1 to 0. The output of the comparator is the output frequency of the frequency divider. UNIVERSITY OF PORTLAND SCHOOL OF ENGINEERING CONTACT: D. BOOTH, J. HAY, P. KELLER THEORY OF OPERATIONS PROJECT CUCKOO Chapter 6 . . . . . . . . . REV. 1.0 PAGE 10 Conclusions In order to improve the design, we might have made the application of the PLL to be something that grabs the attention of the audience more. For instance, having it demodulate a radio signal, or making the signal produce sound. The reset function was added to improve the design as an afterthought, and could possibly be a drastic improvement if the flip-flops had started up in an unknown state and caused errors. In conclusion, this document serves as a manual for the user of the PLL circuit. We discussed the major components, how they are to be used and connected, and the theory of how it operates. We also discussed the theory behind the PLL and some of its uses. The PLL we are currently building should operate in the manner we have outlined in this document. UNIVERSITY OF PORTLAND SCHOOL OF ENGINEERING CONTACT: D. BOOTH, J. HAY, P. KELLER