* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Chapter 29 MEMS

Survey

Document related concepts

Energy applications of nanotechnology wikipedia , lookup

Low-energy electron diffraction wikipedia , lookup

Crystal structure wikipedia , lookup

Flux (metallurgy) wikipedia , lookup

Tunable metamaterial wikipedia , lookup

Self-assembled monolayer wikipedia , lookup

Synthetic setae wikipedia , lookup

Nanochemistry wikipedia , lookup

Silicon carbide wikipedia , lookup

Nanofluidic circuitry wikipedia , lookup

Lithography wikipedia , lookup

Thermal copper pillar bump wikipedia , lookup

Transcript

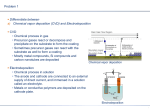

Chapters 28 and 29 April 10, 2006 Group 5 Michael Linley Matt Sallee Bryan Estvanko Patrick Pace Clean Rooms Typical integrated circuits are a few millimeters in length and transistor on the circuit can be only a few nanometers. Clean Room - a room where contaminants (dust, smoke, perfume, and bacteria) are reduced to a very low level by special procedures so that operations can be performed effectively. This is an enlarged image of a grain of salt on a piece of a microprocessor. Clean Rooms There are many different level or classes of clean rooms. The system of classification refers to the number of .5 micrometers (10^-6) or larger particles in within a cubic foot of air. The controlled atmosphere in a clean room is done with ventilation which passes all the air through high-performance particulate air (HEPA) filters. Most clean rooms for microelectronics manufacturing are from class 10 to class 1. Clean Rooms Clean Rooms The greatest source of contaminants in clean rooms, comes from the people who work in them. Skin particles, hair, makeup, clothing and bacteria are given off by humans constantly, due to this fact special covering are required such as lab coats, gloves, hair nets and avoidance of perfume and makeup. Clean Rooms The more stringent clean rooms require people to wear bunny suits. Semiconductors and Silicon Semiconductors are the foundation for electronic devices because their properties can be control by adding impurity atoms. Silicon has become the industry standard in the fabrication of these devices because it’s the second most abundant atom and it can operate at higher temperatures than the alternative germanium. Silicon is a diamond –type fcc structure. Miller indices are used to identify the planes and directions within a unit cell. Crystal Growing and Wafer Preparation Single-crystal material is needed for semiconductor device production. Single-crystal silicon is usually obtained through the Czochralski or CZ process. Crystal Growing and Wafer Preparation A seed crystal is dipped into melted silicon, then is pulled out slowly while being rotated . Controlled amounts of impurities can be added to obtain a uniformly doped crystal. Usually grown larger then needed and ground down to a precise diameter Film Deposition Films are used widely in microelectronicdevice fabrication, especially insulating and conducting films. Epitaxy - is the growth of a vapor deposit, epitaxy or electrodeposit happens when the crystal orientation of the deposit is related directly to the crystal orientation in the crystalline substrate. Film Deposition Advantages of processing on the deposited films instead of on the wafer are fewer impurities, improved performance and the tailoring of material properties. Major functions of the films are masking and protecting the semiconductor surface. In masking The film effectively must inhibit the passage of dopants and display the ability to be etched into patterns of high resolution. Film Deposition Methods of film deposition Evaporation, Metal is heated in a vacuum to its vaporization point. Upon evaporation the metal forms in thin layers on the substrate surface. Sputtering, bombarding a target with high energy ions in a vacuum. As ions impinge on the target, atoms are knocked off and deposited on the wafers. Film Deposition Chemical vapor deposition (CVD), film depositing is achieved by way of reaction or decomposition of gaseous compounds. Oxidation Growth of an oxide layer as a result of the reaction of oxygen with the substrates material. Can also be formed using deposition techniques Thermally grown oxides (dry, wet, and selective) have higher level of purity than deposition Dry Oxidation Simple Process Elevated Temperatures (usually around 750º to 1100º C (1300º to 2200º F)) Ratio of oxide thickness to the amount of silicon consumed is 1:0.44 Wet Oxidation Utilizes water vapor atmosphere as an agent. Higher growth rate than dry oxidation. Lower oxide density (therefore lower dielectric strength) Dry-Wet-Dry Selective Oxidation Oxidizes only certain portions of the surface Uses silicon nitride. Lithography Process by which the geometric patterns that define devices are transferred to the substrate surface. Types: Ultraviolet (Photolithography), Xray, and Electron beam. Ultraviolet (Photolithography) Most widely used Uses reticle (photomask or mask) Reduction lithography Photoresist Prebaking/Postbaking Stripping Ashing Line Width Extreme Ultraviolet Light diffraction Wavelength of 13 nm Features in range of 30 to 100 nm Highly reflective molybdenum –silicon mirrors. X-ray Lithography Superior to photolithography Aspect ratio of more than 100 LIGA Process Electron-beam Lithography Superior to Photography Resolution limited to 10 nm Very expensive Slower in Scanning time SCALPEL Scattering with angular limitation projection electron-beam lithography Small sized marks High potential Lithography Techniques Method Wavelength (nm) Finest Feature Size (nm) Ultraviolet (Photolithography) 365 350 Deep UV 248 250 Extreme UV 10 to 20 30 to 100 X-ray 0.01 to 1 20 to 100 ----- 80 Electron beam Etching Process by which entire films or particular sections of film are removed. Selectivity Wet etching and dry etching Wet Etching Immersing the wafers in a liquid solution, usually acidic. Isotropic Effective etching requires certain conditions. Isotropic Etchants Many different uses Strong acids Size of the features Anisotropic Etching Takes place when etching is strongly dependent on compostional and structural variations in the material. Orientation-dependent etching and Vertical etching Anisotropy ratio (AR = E1/E2) Etch stop (Boron etch stop) Back etching Dry Etching Involves the use of chemical reactants in a low-pressure system. High degree of directionality, resulting in highly anisotropic-etching profiles Requires small amounts of the reactant gases. Usually involves a plasma or discharge in areas of high-electric and magnetic fields. Sputter Etching Removes material by hitting it with noble gases (usually argon). Concerns with sputter etching. Reactive Plasma Etching Also called dry chemical etching Involves chlorine or fluorine ions and other molecular species that diffuse to and chemically react with substrate, forming a volatile compound which is removed by the vacuum system. The Process Physical-Chemical Etching Two types: Reactive ion-beam etching (RIBE) and Chemically assisted ion-based etching (CAIBE) Combines physical and chemical etching Ion bombardment helps assist dry chemical etching Ion bombardment is directional, ionbombardment energy is low and does not contribute much to mask removal Very large aspect ratios Cryogenic Etching Deep features with vertical walls Low temperatures The Process Diffusion and Ion Implantation Diffusion 800º to 1200º C (1500º to 2200º F) Drive-in diffusion Ion Implantation 400º to 800º C (750º to 1500º F) 28.10 Metallization and Testing Interconnections- are made with metals that exhibit low electrical resistance and good adhesion to dielectric insulator surfaces. Aluminum and Aluminum-copper alloys are most commonly used for interconnections. Electromigration- process where aluminum atoms are moved physically by the impact of drifting atoms under high-current conditions. Solutions a) addition of sandwiched metal layers such as tungsten or titanium. b) use pure copper which has better properties to resist electromigration. Connection levels Level 0: transistor within an IC Level 1: ICs, other discrete components Level 2: IC packages Level 3: printed circuit boards Level 4: chassis or box Level 5: system or computer Interconnection patterns are produced by etching or lithographic processes. •Modern ICs normally have one to six layers of metallization and each metal layer is insulated by a dielectric. •Planarization- process of producing a planar surface. – Planarization is critical for the dielectric layers to reduce metal shorts and linewidth variations of the interconnections. –Done by chemical-mechanical polishing (CMP) –Accurate to 1.2 X 10-6 in of being perfectly flat. •The layers of metals are then connected by vias. •Access to these devices is made possible through contacts. •The wafer is complete once a layer of silicon nitride is added to provide scratch resistance. Testing of the dies Next, all the individual currents on the chip are tested by a small probe in one of two ways: 1. Test patterns or structures: the probe measures test structures on scribe lines that record various bits of information. 2. Direct probe: uses 100% testing on the bond pads of each die. After Testing If a chip fails a test it is marked with a drop of ink. Back grinding may take place to remove some of the original substrate. After back grinding, diamond sawing is used to cut each die out of the wafer. The dice are then sorted by functional and non functional. The non functional dice are discarded while the functional dice are sent for packaging. 28.11 Wire Bonding and Packaging Working dice must be attached to a more secure foundation. The die is then attached to the packaging with epoxy cement or by an eutectic bond. After being attached, the chip must be electrically connected to the substrate. Wire bonding: is the process of attaching very thin gold wires from the packaging lead to the bonding pads located on the chip. Final Packaging The chip is now ready for final packaging. There are many ways the chip can be packaged and the type of packaging largely impacts the cost of the chip. Package considerations: chip size, number of external leads, operating environment, heat dissipation, and power requirements. Packages can be produced from polymers, metals, or ceramics. Metal Packages Produced from alloys like Kovar. Provide a hermetic seal and good thermal conductivity. Limited number of leads that can be used. Plastic Packages Very inexpensive and have high lead counts. Have high thermal resistance but not hermetically sealed. Ceramic Packages More expensive Usually produced from Al2O3. Have hermetic seal and have good thermal conductivity. Higher lead counts than metal and lower lead counts than plastic. Kinds of Packages Dual-in-line Package (DIP) Low cost ease of handling Modular design Flat Package Flat, low profile, leads on same plane Permanente, not Modular Used in multiple-level circuit boards Surface Mount Package Chip is slightly above board and soldered to it Pin-Grid Arrays (PGAs) Tightly packed pins that connect by way of through-holes onto printed circuit boards. Susceptible to plastic deformation Solution: Ball-Grid Arrays (BGAs) Many tiny little balls connected on the underside of the package that are evenly spaced. The package is reflow soldered to the circuit board, adding rigidity. More Testing After the chip is sealed in its package it undergoes final testing. The tests make sure the chip is sealed off from the environment. The testing tests for: heat, humidity, mechanical shock, corrosion, and vibration. Destructive tests are also performed to investigate the effectiveness of sealing. 28.13 Printed Circuit Boards A printed circuit board is the substrate for the final interconnections among all of the completed chips. Circuit boards can contain: resistors, capacitors, inductors, high-performance, transistors, large capacitors, precision resistors, and crystals. A printed circuit board is a plastic material containing several layers of copper foil. There are single sided boards, double sided boards, and multi-layer boards. Building the Boards The boards are sheared to a desired size and locating holes are drilled or punched in them. Holes for vias or connections are drilled by a CNC. Multiple boards can be drilled at one time due to the precision of the CNC. The conductive patterns are defined by lithography (originally screen printed). Methods of Laying Conductive Paths Subtractive method: copper foil bonded to the board. Desired pattern is defined with a positive mask by photolithography and the rest is removed by wet etching. Additive method: a negative mask is placed on the board to define the desired shape. Electroless plating and electroplating of copper serve to define the connections, tracks, and lands on the circuit board. Design Considerations for PCBs 1. Wave soldering should be used only on one side of the board. 2. IC packages should be laid out carefully on the printed circuit board. 3. Allow room between ICs to provide sufficient cooling requirements. 4. Leave enough room around ICs to allow for reworking and repairing without causing more damage. Chapter 29 MEMS microelectromechanical devices and systems What are they? They are devices the size of a pinpoint that combine electrical and mechanical elements such as: SMALL ELECTRIC TWEEZERS SMALL SENSORS (( Micrometer = 1x10^-6 m )) MANUFACTURING PROCESS Bulk Micro-Machining Older method but still prevalent. Simpler Shapes Surface Micro-Machining This method has more steps, and can create more complex shapes. The processes in CH28 are semiConductor based, MEMS do not have the Same restriction. Bulk Machining Uses orientation dependant etching, and single crystal silicon. Some enchants will eat along the planes of a crystal. Diffuse with p-type silicon Place a mask – silicon nitride Etch the mask And silicon base Block to leave cantilever Surface Micromachining Deposit phosphosilicate glass by chemical Vapor deposition, can be removed by HF acid Put on a mask, etch the PSG, then Remove the mask. Deposit Polysilicon, which is the finished Shape. Remove the unwanted PSG to finish the Part. Surface Micromachining produces more complex parts. Applications Hinges can be used for such applications As micromirrors for use in High Definition TV’s. Applications Micro-grabbers and tweezers Movie of MEMS in action