* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download DC load line - UniMAP Portal

Oscilloscope history wikipedia , lookup

Josephson voltage standard wikipedia , lookup

Index of electronics articles wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Regenerative circuit wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Schmitt trigger wikipedia , lookup

Standing wave ratio wikipedia , lookup

Radio transmitter design wikipedia , lookup

Surge protector wikipedia , lookup

Two-port network wikipedia , lookup

Voltage regulator wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Power MOSFET wikipedia , lookup

Current source wikipedia , lookup

Operational amplifier wikipedia , lookup

Power electronics wikipedia , lookup

Audio power wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Negative-feedback amplifier wikipedia , lookup

Valve audio amplifier technical specification wikipedia , lookup

Current mirror wikipedia , lookup

Opto-isolator wikipedia , lookup

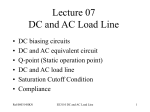

POWER AMPLIFIER (Additional Lecture Notes) EKT 104 DC and AC Equivalent Circuits +VCC +VCC IC RC RC R1 R1 RL vce vin vin R2 R2 RE R1//R2 IE RE rC = RC//RL Bias Circuit DC equivalent circuit AC equivalent circuit rC Load Lines • Every amplifier has two loads: a DC load and an AC load. • DC load line– all possible DC combinations of IC and VCE. • AC load line – all possible AC combinations of iC and vCE. • AC load line involves Rc||RL in its determination, hence it is steeper than the DC line *Q point is shared by both DC and AC load lines. However, it is determined on the DC load line. DC Load Line IC(sat) = VCC/(RC+RE) The straight line is known as the DC load line DC Load Line IC (mA) The collector current IC and the collectoremitter voltage VCE must always lie on the load line, depends ONLY on the VCC, RC and RE (i.e. The dc load line is a graph that represents all the possible combinations of IC and VCE for a given amplifier. For every possible value of IC, and amplifier will have a corresponding value of VCE.) VCE(off) = VCC VCE What is IC(sat) and VCE(off) ? Purpose of the DC biasing circuit • To turn the device “ON” • To place it in operation in the region of its characteristic where the device operates most linearly, i.e. to set up the initial dc values of IB, IC, and VCE DC Biasing Circuits The ac operation of an amplifier depends on the initial dc values of IB, IC, and VCE. +VCC By varying IB around an initial dc value, IC and VCE are made to vary around their initial dc values. DC biasing is a static operation since it deals with setting a fixed (steady) level of current (through the device) with a desired fixed voltage drop across the device. v in RC RB v out ib vce ic Q-Point (Static Operation Point) • When a transistor does not have an ac input, it will have specific dc values of IC and VCE. • These values correspond to a specific point on the dc load line. This point is called the Q-point. • A quiescent amplifier is one that has no ac signal applied and therefore has constant dc values of IC and VCE. Q-Point (Static Operation Point) • The intersection of the dc bias value of IB with the dc load line determines the Q-point. • It is desirable to have the Qpoint centered on the load line. Why? • When a circuit is designed to have a centered Q-point, the amplifier is said to be midpoint biased. • Midpoint biasing allows optimum ac operation of the amplifier. 8 DC Biasing + AC signal • When an ac signal is applied to the base of the transistor, IC and VCE will both vary around their Q-point values. • When the Q-point is centered, IC and VCE can both make the maximum possible transitions above and below their initial dc values. • When the Q-point is above the center on the load line, the input signal may cause the transistor to saturate. When this happens, a part of the output signal will be clipped off. • When the Q-point is below midpoint on the load line, the input signal may cause the transistor to cutoff. This can also cause a portion of the output signal to be clipped. DC Biasing + AC signal 10 AC Load Line What does the ac load line tell you? • The ac load line tells the maximum possible output voltage swing for a given amplifier---- the maximum possible peak-to-peak output voltage (Vpp ) from a given amplifier. • The maximum undistorted Vpp is referred to as the compliance of the amplifier. • The smaller of the two swings limits the maximum undistorted collector current for a given amplifier. AC Load Line IC(sat) = VCC/(RC+RE) DC Load Line IC (mA) VCE(off) = VCC VCE • The ac load line of a given amplifier will not follow the plot of the dc load line. • This is due to the dc load of an amplifier is different from the ac load. IC(sat) = ICQ + (VCEQ/rC) ac load line ac load line IC IC Q - point dc load line VCE(off) = VCEQ + ICQrC VCE VCE * (AC Saturation Current Ic(sat) , AC Cutoff Voltage VCE(off) ) AC Load Line: The Upper Swing • The current can swing from the Q point value to ic(sat). - In this example, from 1.1mA to 3.52 mA. • vCE can change from the Q point value to zero. - In this example, from 4.94 V to 0 V. AC Load Line: The Lower Swing • The current can swing from the Q point value to zero. - In this case, from 1.1mA to 0 mA. • vCE can change from the Q point value to vCE(off). - In this example, from 4.94 V to 7.18 V. • The voltage swing is determined by ICQrC. - In this case, the maximum value of ICQrC is (1.1 mA)(2.04k Ohm)=2.24 V. * This means that as the collector current swings between 1.1 mA and zero, the value of vCE will vary from 4.94 V to 7.18 V Calculating Compliance • The smallest of the two (upper swing and lower swing) determines the maximum possible peak voltage that can pass undistorted throughout our amplifier. • In the example, the maximum upper swing peak voltage is 4.94 Vpk and the minimum lower swing peak voltage is 2.24 Vpk . • Two times of the maximum possible peak voltage will give the maximum peak-to-peak transition value of the output voltage. Calculating Compliance • • • • • The maximum peak-to-peak swing is given by: PP=2VCEQ OR PP=2ICQrC In the example, max peak-to-peak value is: 2(4.94 Vpk)=9.88 Vp-p OR 2(2.24 Vpk)= 4.48 Vp-p Since 4.48 Vp-p is the smaller of the two---it is the compliance of the amplifier. The Q point is below the mid-point of AC load line. Cutoff clipping happens when the output voltage exceeds the compliance of the amplifier as shown in Waveform (A). Waveform (B) is limited to the compliance of the circuit (4.48 Vp-p)---it is not clipped and is undistorted. Cutoff Clipping • The Q point is below the midpoint and the output voltage is clipped off at the value of Vce(off). Cutoff Clipping Saturation Clipping • The Q point is above the midpoint and the output voltage is clipped off when the amplifier hits saturation. At this point, the value of Vce Is virtually 0. Vce(off) Saturation Clipping Efficiency • The ideal power amplifier would deliver 100% of the power it draws from the power supply to the load. • We know that this is not true and that components in the amplifier will all dissipate some power that is being drawn from the supply. Where PL h = *100 PS PL = average ac power to the load PS = average power supplied by the source (VCC) AMPLIFIER DC POWER • The DC source supplies direct current to the voltage divider and to the collector circuit. • The total supply current is the divider current plus the quiescent collector current. ICC=ICQ+I1 • The total dc power that the amplifier draws from the power supply is found as: Ps=VCCICC AC Load Power • The ac load power is the power that is transferred to the load. • The ac load power can be calculated as follows Exercise 1 • For the transistor in the commonemitter circuit in Figure Ex. 1, the parameters are: β=80, PD,max =10W, VCE(sus) =30V, and IC,max =1.2A. • (a) Design the values of RL and RB for VCC = 30 V. What is maximum power dissipated in the transistor? • (b) Using the value of RL in part (a), find IC,max and VCC if PD,max = 5 W. • (c) Calculate the maximum undistorted ac power that can be delivered to RL in parts (a) and (b) for the assumption that iC ≥0 and 0≤vCE ≤VCC. Figure Ex.1 Exercise 1: Solution (a) Exercise 1: Solution (b) Exercise 1: Solution (c)