* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Charge pump: adaptive hysteretic control with modular switches

Spark-gap transmitter wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Regenerative circuit wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Radio transmitter design wikipedia , lookup

Josephson voltage standard wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Two-port network wikipedia , lookup

Valve audio amplifier technical specification wikipedia , lookup

Power MOSFET wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Wilson current mirror wikipedia , lookup

Current source wikipedia , lookup

Integrating ADC wikipedia , lookup

Operational amplifier wikipedia , lookup

Surge protector wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Power electronics wikipedia , lookup

Voltage regulator wikipedia , lookup

Schmitt trigger wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Current mirror wikipedia , lookup

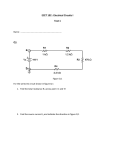

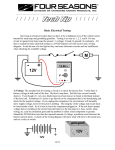

Charge pump: adaptive hysteretic control with modular switches Ricardo Madureira Valter Sádio Marcelino Santos IST-UTL Lisbon, Portugal [email protected] IST-UTL / INESC-ID Lisbon, Portugal [email protected] IST-UTL / INESC-ID, Silicongate Lisbon, Portugal [email protected] Abstract— A charge pump boost converter is proposed. To achieve an acceptable output voltage ripple without jeopardizing transient response and start-up time, a method of parallelizing switches is used, controlled by a Mealy machine. The result is an adaptive hysteretic control that uses modular switches. With light loads, the number of modules is reduced to one per switch. During high current load transients, all modules are used, thus tripling the output current capability. The proposed charge pump supplies a regulated voltage of 3.3V, from an input voltage of 2.5V. The IP includes soft-start (inrush current limitation), soft-recovery and short-circuit protection on all output pins. It was designed with TSMC 130nm LowPower technology. Keywords — charge pump; switched capacitors; hysteretic control; digital control; inrush current; soft-recovery; controlled start-up I. INTRODUCTION To implement a charge pump able to convert 2.5V into 3.3V, a voltage doubler structure was used, showed in Fig.1. In a voltage doubler charge pump, transient response is limited by the output equivalent resistance [1], given by (1). Vin Rsw2 Rsw1 Cfly Rsw4 Rsw3 Vout switcher’s resistance or the flying capacitor (CFLY in Fig.1 and in equation (1)). The maximum efficiency of the charge pump doubler is presented in (2) and the voltage ripple [2] depends on the frequency of operation, current load and output capacitance (3). (2) (3) The current consumption of the driving circuit of the charge pump is, typically, the most significant and must be minimized to achieve higher efficiency. This consumption is proportional to the capacitance of the driver’s stage, to the frequency of operation and to the square of the driving voltage. This last parameter must be equal to the highest voltage available in the circuit, to properly turn ON and OFF the PMOS switches. Lowering the frequency of operation or the driving stage capacitance (including the main switch) is possible. But, lowering the frequency of operation will increase voltage ripple, and less driving capacitance will limit the transient response of the charge pump, by limiting the output resistance to a higher value. The solution proposed in this work is to divide the switches, enabling low ripple and fast transient response. Cout II. CONTROL METHOD Fig. 1. Voltage doubler topology. (1) This resistance is modulated to achieve output voltage regulation by varying the frequency of operation, the Several methods are used nowadays to regulate output voltage in charge pumps, each with advantages and disadvantages. Constant frequency control [1] with two sequenced phases of operation is used with a transconductance amplifier that compares the output voltage with a voltage reference and controls the amount of charge injected in the flying capacitors. The output capacitor is charged when the output voltage is too low. This control scheme has a well defined noise frequency spectrum that can be filtered, but has poor efficiency with light loads. Current mode control [3, 4] can be implemented with a current sensing circuit, usually a series sensing resistor, with large power loss, or with a current sensing transistor in parallel with the power transistor that demands additional circuitry. This kind of control is used with duty cycle close to conversion ratio to achieve low output voltage ripple in high load conditions. Pulse Skipping [5,6] is used with constant switching frequency and constant duty cycle with charge and discharge modes of operation. The charge pump operates on charge mode when the output voltage drops below a predetermined threshold voltage, otherwise operates with minimum supply current in discharge mode, where the output capacitor supplies charge to the load. This control method is very good to improve efficiency with light loads and has fast response to load variations but produces high output voltage ripple. Burst Mode [7] is a control methodology that, when the load current load is less than a prescribed threshold, the clock is turned on and off for a number of clock cycles that depend on the current absorbed by the load. This method allows high efficiency with light loads but produces high output voltage ripple and high tonal spectrum. The solution proposed in this work is to divide the switches, so that for lower output currents only 1/3 of the switching strength is used, and for higher currents or during transients, full switching strength is used. This way, driver capacitance is reduced for most of the output current range of the charge pump. To further increase efficiency, a break before make circuit is used to drive the main switches. A PMOS switch module, in Fig.2, and a NMOS switch module, in Fig.3, were designed, that include the driving circuit, driven by low voltage digital signals. These modules can be parallelized in different number. In the proposed charge pump, they were combined in triplets, for each charge pump switch. During normal operation only one module per switch is activated. Whenever the current demand is higher, all three are used. The control was implemented with a Mealy machine. If the output is low during two or more pumping periods, all switches are used. If the output voltage stays higher than the desired value for less than two pumping cycles, only one switch is used. This method allows reducing the output resistance of the charge pump to one third for load transients, thus improving dynamic response. In the diagram presented in the Fig. 4 the box Switch Module represents either a PMOS switch or an NMOS switch, depending on the relevant phase. Two slightly different blocks were design for Sw2 position. The difference is that the PMOS module switches in this position must allow being current limited, so that they can behave like current sources during start-up, short-circuit and soft-recovering events. Low voltage domain (DVDD) Highest voltage domain (Vin if Vout < Vin or Vout if Vout > Vin) Mp1 Feedback to digital ctrl block Mn1 Non-overlap circuit avoids shoot-through current in the driver Fig. 2. Simplified PMOS module circuit diagram. Highest voltage domain (Vin if Vout < Vin or Vout if Vout > Vin) Low voltage domain (DVDD) Mp1 Crtl input Feedback to digital ctrl block Mn1 Non-overlap circuit avoids shoot-through current in the driver Fig. 3. Simplified NMOS module circuit diagram. Vout Cout Phase Generator Feedback comparator switch module + switch module Z Vref -1 switch module Fig. 4. Simplified block diagram of the main control circuit. III. ANCILLARIES A. Highest voltage selection The PMOS switching devices must be biased and driven by the highest voltage available in the circuit. During start-up the highest voltage available is VIN, after that, VOUT is the highest one. Therefore, a voltage selection circuit must be used. For bulk biasing, a simple OR diode circuit is enough, but to properly supply the driving circuitry, a low impedance selection circuit is needed. Fig. 5 presents the block diagram of the voltage selection circuit. A passive OR circuit is used in parallel with an active OR circuit. The impedance of the selection devices is such that allows the driven circuit to operate without significant voltage drops. B. Soft-start, short-circuit protection and soft-recovery When the charge pump is first turned on, the flying and output capacitors can be fully discharged. This means that when the switches are closed in order to charge the flying capacitor and when they change to the second phase, to transfer the charge do the output capacitor, the voltage difference will be high. This high voltage difference will originate current peaks in the order of VIN/RSW, which can reach several amps. Also, when supplying digital cores, it is important to control the ramp-up output voltage, so that the digital circuits start properly. To limit the in-rush current and to ramp the output voltage the following method is used. available in the circuit, in this situation, V IN. Also that is the voltage applied to the Sw2 source terminal, therefore, it remains saturated. The same circuit also gives short-circuit protection for all output pins of the charge pump. When the output current increases beyond regulation limits, the output voltage begins to fall, due to the output resistance of the charge pump. When the output voltage falls below VIN less a threshold voltage, the current limitation circuit is engaged and switches are forced to the start-up position. This mechanism protects the circuit from short-circuits in the load and in the capacitors. Mp1 A comparator will sense the output and input voltages. If the output voltage is lower than the input voltage, the comparator output signals the control block to enter in startup mode. ‘1’ Sw2 Mn1 Passive OR ‘0’ Vhigh Vin Vin Vout Active OR Vout Vin Comparator Levelshifter with shcmitt-trigger Fig. 7. Switch 2 current limitation. Fig. 5. Highest voltage selection circuit. Vin Rsw1 Rsw2 Rsw3 Rsw4 To control block Start-up comparator output + Vout Vreg Start-up comparator Vbulk Vin Fig. 6. Start-up comparator. When signaled to enter start-up mode, the control block will close switches 3 and 4, putting CFLY and COUT in parallel, and limit the current capability of switch 2. The control voltage applied to the gate of this switch is limited by the circuit presented in Fig. 7. The current limit is configurable, in order to control the start-up time with different external capacitances. The driving transistors Mp1 and Mn1, in Fig.7, are turned off and the Sw2 is forced into saturation [8]. The current reference circuit is supplied by V IN, so the output voltage is compared with VIN less a threshold voltage, in Fig. 6, to ensure that the internal reference currents do not lose compliance. The driving voltage is the highest voltage Vreg Vout Vin-Vth Continuous charge t=(Vin - Vth).(Cout + Cfly) / Ilimit Discrete charge τ=(Rout)Cout Fig. 8. Start-up sequence. To lower the current consumption during normal operation, the start-up comparator is shut-down by the highest voltage selection circuit. Whenever the output voltage becomes higher than VIN, start-up circuit is disabled. C. Feedback voltage circuit The feedback voltage comparator used in the proposed charge pump is a standard clocked comparator. The comparator uses low voltage transistors, thus the reference voltage is not the usual bandgap voltage of approximately 1.2V but only 600mV. Also due to the usage of low voltage transistors, the inputs of the comparator are clamped by diode connected high voltage NMOS, to protect them from higher voltages. latch latch other input, coming from a voltage reference circuit, has also low impedance at moderate frequencies. The capacitors are formed by fingered metal layers placed on top of the poly resistors from the resistive voltage divider, so no extra silicon area is needed. (3) The feedback circuit is trimmed, and provides two extra output voltages: Vsnshigh and Vsnslow. These voltages are used by an external comparator, sharing the same 600mV reference voltage, to assert a Vok signal. outp outn reset vp vn Vsns latch resetz latch C1 R1 C2 R2 Vsnshigh Vfb HV HV Clamping Output voltage comparator Vsnslow Cin Fig. 9. Output voltage feedback comparator. 3:8 decoder Trim[0:2] Fig. 11. Output voltage feedback. clk reset latch ( resetz ( ) ) ( ) (4) Fig. 10. Reset and latch generation. To reduce kick-back to the inputs, a complementary switch is used to perform the reset of the internal nodes of the comparator. By using complementary switches, the charge injection of each one, when they are turned ON or OFF, is canceled by each other. Due to process variations, reset and latch phases can become off 180º phase. To guarantee that the latch phase always start after the completeness of the reset phase a starved inverter is used to generate it , presented in Fig. 10. The output of the voltage comparator is held by a standard latch circuit, during the reset phase. The output voltage is sensed by a compensated voltage feedback resistive divider, as presented in Fig.11. Two capacitors are placed in parallel with the two branches of the resistive divider with two proposes. First, they allow compensating the capacitance effect of the input node of the comparator that would otherwise form a pole in the sensing circuit at a frequency given by (3). Secondly, these capacitors will raise the capacitance seen by the input of the comparator, therefore reducing kickback effects. It is assumed that the (5) To compensate the response of the resistive divider, the capacitance in the lower branch, formed by the added capacitance plus the input capacitance of the comparator (5), must be equal to C1*(R1/R2) (4). E. Vok and UVLO Two important signals are commonly used with switched regulators: Vok and UVLO. Vok is asserted when the output voltage is within certain limits of the desired voltage. This allows to start-up the supplied circuit only when the supplying circuit is fully operational. In the proposed charge pump this signal is generated with a comparator with hysteresis, which shares the same voltage divider of the charge pump, taking advantage of the two additional voltages Vsnshigh and Vsnslow. Fig. 12 presents the block diagram of the comparator with hysteresis. Vsnslow Vsnshigh - Vok + Vref Averaged input current. Fig. 12. Vok generator circuit. Vin + UVLOz - en Vsnshigh Vref UVLO Vsnslow Fig. 15. Start-up simulation. dvdd Vbgok Fig. 13. UVLO generator circuit. UVLO signal is used to disable the charge pump operation when the input voltage V IN is not high enough to sustain the proper operation of the circuit. The objective is to avoid erratic behavior of the switching circuit. This signal is of utmost importance when no soft-start circuit is used. When VIN is ramping up, without a soft-start circuit the switching regulator will soon start to demand high peak currents from the supply voltage. These peak currents can interfere with the ramp up of the input voltage and cause oscillations during start-up. Despite the inclusion of a start-up circuit, it was decided to implement also an UVLO circuit. IV. Results The circuit was simulated using HSPICE. In the simulation results, presented below, ideal 1uF and 100nF flying and output capacitors were used. Input voltage is 3.3V (TYP), 2.25V (MIN) and 2.94V (MAX). The external frequency supplied to the charge pump is 1 MHz. Fig. 16. Short-circuit protection and soft-recovery. Fig. 15 presents the average input current during start-up (middle plot). Fig. 16 presents an output short-circuit, followed by soft-recovery. The load of 330Ω is shortcircuited during 100µs. The upper plot shows the output voltage, the middle plot shows the current in the load and the third plot shows the input current. Fig. 17 presents the transient response from 1mA to 10mA. Table I resumes the obtained results. Fig. 17. Load transient from 1mA to 10mA. Table I. Simulation results Parameter ACKNOWLEDGMENT MIN TYP MAX Unit Output Voltage 3.15 3.3 3.45 V Output Voltage Accuracy -5 - +5 % Output voltage ripple (1 mA) - - 20 mVpp Output voltage ripple (10 mA) - - 60 mVpp In rush and short-circuit current (programmable) 25 - 150 mA Start-up time - 100 200 s Load Transient (1-10mA) - 2 - mV/mA Load Regulation (0-50mA) - 0.8 - mV/mA Quiescent current - 5 10 A (no load) Efficiency 65 % Core area (Excluding Vok/UVLO circuits and PADS) - 0.13 - mm2 V. Conclusions An adaptive hysteretic control that uses modular switches was proposed. With light loads, the number of modules is reduced to one per switch. During high current load transients, all modules are used, thus tripling the output current capability. The proposed charge pump supplies a regulated voltage of 3.3V, from an input voltage of 2.5V. It was designed to provide a maximum permanent output current of 10mA. When operating at full strength, the output current capability extends to more than 30mA. Output voltage ripple with low ESR capacitors (20mΩ) of 1μF and 100nF (COUT and CFLY) is 20mV with 1mA load current and 60mV with 10mA load. The typical efficiency with maximum output current is 65%, 98% of the maximum theoretical value. The quiescent current without load is less than 10μA. The typical power dissipation at full load is 17.8 mW. The IP includes soft-start (in-rush current limitation), soft-recovery and short-circuit protection on all output pins. It was designed with TSMC 130nm LowPower technology. This circuit can be used in standard applications like USBOTG 3.3V. This work was partially funded by the Portuguese National Foundation of Science and Technology through the project PTDC/EEA-ELC/113902/2009 and through the PIDDAC Program funds (INESC-ID multiannual funding). REFERENCES [1] B. Robert Gregoire, “A Compact Switched-Capacitor Regulated Charge Pump Power Supply”, IEEE Journal of Solid-state Circuits, vol. 41, pp. 1944-1953, August 2006. [2] Jae-Youl Lee et al, “A Regulated Charge Pump With Small Ripple Voltage and Fast Start-Up”, IEEE Journal of Solid-state Circuits, vol. 41, pp. 425-432, February 2006. [3] Shao Bin; Yang Yujia; Wang Ying; Hong Zhiliang, “High Efficiency, inductorless step-down DC-DC converter”, ASIC, 2005, ASICON 2005. 6th International conference, vol. 1, no., pp. 395-398, 24-0 Oct. 2005. [4] Cheung Fai Lee; Mok, P.K.T., "A monolithic currentmode CMOS DC-DC converter with on-chip current-sensing technique," Solid-State Circuits, IEEE Journal of , vol.39, no.1, pp. 3-14, Jan. 2004. [5] Saiz-Vela, A.; Miribel-Catala, P.; Puig-Vidal, M.; Samitier, J., "An electron mobility independent pulse skipping regulator for a programmable CMOS charge pump," Circuits and Systems, 2005. ISCAS 2005. IEEE International Symposium on , vol., no., pp. 117-120 Vol. 1, 23-26 May 2005. [6] Valter Sádio; Abílio Parreira; Marcelino Santos, "A 100mA fractional step-down charge pump with digital control," Proc. SPIE, vol. 7363, May 2009. [7] Budaes, M.; Goras, L., "Burst Mode Switching Mechanism for an Inductorless DC-DC Converter," Semiconductor Conference, 2007. CAS 2007. International, vol.2, no., pp.463-466, Oct. 15 2007-Sept. 17 2007. [8] Erich Bayer, Hans Schmeller, “Charge Pump with Active Cycle Regulation – Closing the Gap between Linear and Skip Modes”, Power Electronics Specialists Conference, vol. 3, pp. 1497-1502, June 2000.